## **User Manual**

## DDOM-SST-XG-44P Manual

Version 3.0 February. 2022

**ICOP** Technology Inc.

## Copyright

The information in this manual is subject to change without notice for continue improvement in the product. All rights are reserved. The manufacturer assumes no reasonability for any inaccuracies that may be contained in this document and makes no commitment to update or to keep current the information contained in this manual.

No part of this manual may be reproduced, copied, translated or transmitted, in whole or in part, in any form or by any means without the prior to written permission of ICOP Technology Inc.

Copyright © 2022 ICOP Technology Inc

## **Trademarks Acknowledgement**

DDOM-SST-44P is the registered trademark of DM&P Electronics Inc. Other brand names and product names that appear in this document are the properties and registered trademarks of their respective owners. All names mentioned herewith are served for identification purpose only.

## **Revision History**

| Revision | Date          | Remark                |

|----------|---------------|-----------------------|

| 1.0      | June 2008     | First version release |

| 2.0      | August 2008   | Update Datasheet      |

| 3.0      | February 2022 | Capacities update     |

## **Table of Contents**

| 1  |     | Product Information                      | 1  |

|----|-----|------------------------------------------|----|

| 1  | .1  | Features                                 | 2  |

| 1  | .2  | Specifications                           | 3  |

| 1  | .3  | Ordering Information                     | 4  |

| 2  |     | Hardware Information                     | 5  |

| 2  | .1  | Pin Assignment                           | 5  |

| 2  | .2  | Signal Descriptions                      | 6  |

| 2  | .3  | System Power Consumption                 | 7  |

| 3  |     | Product Model and Physical Specification | 8  |

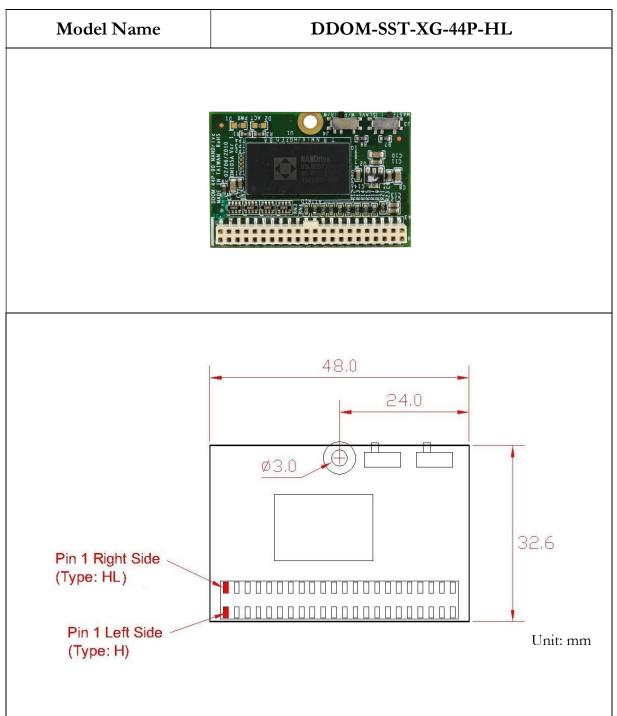

| 3  | .1  | 44 Pin Horizontal Right Side             | 8  |

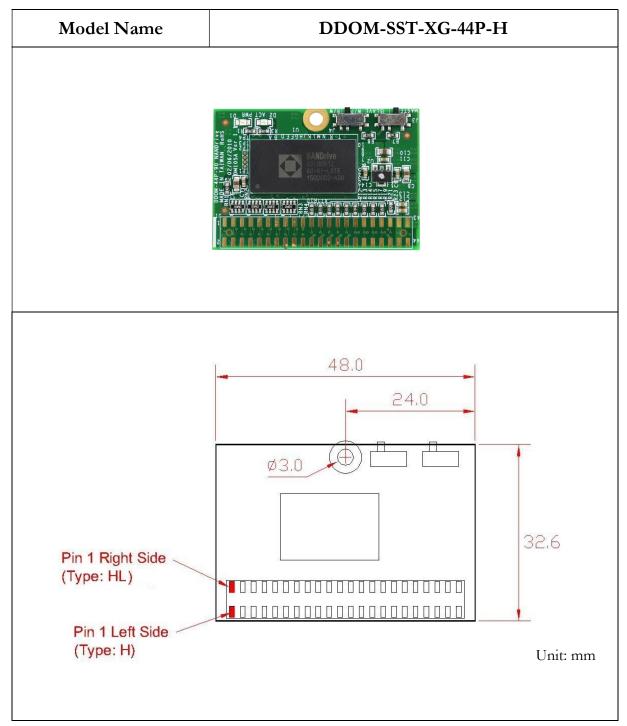

| 3  | .2  | 44 Pin Horizontal Left Side              | 9  |

| Wa | ırı | anty                                     | 10 |

## **1 Product Information**

#### Dependable and Secure

Designed with advanced IDE flash controller technology, DDOM-SST-XG-44P is 100% compatible with the standard IDE/ATA storage interface without the need for special device driver. This advanced IDE flash controller's multi-tasking integrated error-detection, error-correction, re-mapping and wear-leveling technologies with power hold-up circuit greatly improves data reliability. Its low-power requirement, advanced PIO modes, multi-sector transfer support and LBA addressing can satisfy application with high performance and reliability requirements.

#### Anti Shock & Anti Vibration

Using advanced solid-state storage technology, without moving parts, DDOM-SST-44P is able to perform all of its designated function without being affected by shock and vibration.

#### Wide Operating Temperature

DDOM-SST-XG-44P is designed to support commercial and industrial applications operating in environment exposed to extreme temperature range. The DDOM-SST-XG-44P series supports -40°C to +85°C operating temperature.

#### 1.1 Features

- -40 °C to +85°C extreme temp range

- Power & Active LEDs, easy to check work status

- RoHS Compliant

- Industrial grade connector, avoid inaccuracy connection

- Write Protect

- Low power operation

- Fixed hole layout

- Unitized 44 pin IDE

- ECC for exceptional data reliability

- Completely solid state no moving parts

- Entirely bootable for current embedded O/S

- 50G/10ms operating shock

- $5G(7 \sim 2000 \text{Mz})$  operating vibration

- 30 MB/s burst R/W rate

- 10 years data integrity

### 1.2 Specifications

| IDE Transfer Mode  | PIO Mode 0-6 / MwDMA Mode 4 / Ultra DMA Mode 0~4    |  |

|--------------------|-----------------------------------------------------|--|

| Drive Config.      | Switch Master/Slave                                 |  |

| Data Transfer Rate | Read 30 Mbytes(Max)/sec<br>Write 20 Mbytes(Max)/sec |  |

| Bus Interface      | ATA Compatibility                                   |  |

| Flash Type         | SLC                                                 |  |

| Connector          | 44pin IDE/ATA ANSI Standards                        |  |

| Storage Capacity   | 1GB / 2GB                                           |  |

| Sector Size        | 512 bytes                                           |  |

| Drive Number       | Drive 0 or 1                                        |  |

| Operation Temp.    | -40°C∼+85°C                                         |  |

| Storage Temp.      | -65°C~+150°C                                        |  |

| Humidity           | 10%~95% non-condensing                              |  |

| Vibration          | 5G (7~2000Hz)                                       |  |

| Shock              | 50G/10ms                                            |  |

| ECC Technology     | High Reliability based on the internal ECC function |  |

| MTBF               | >3,000,000 hours                                    |  |

| R/W Endurance      | 2,000,000 times                                     |  |

| Wear-leveling      | Support                                             |  |

| Data Integrity     | 10 years                                            |  |

| DC Input Voltage   | +3.3V / +5V single power supply operation           |  |

| Power Mode         | Auto Stand-by and sleep mode                        |  |

### 1.3 Ordering Information

| PART NO.           | Capacities | Туре             | Operation Temp. |

|--------------------|------------|------------------|-----------------|

| DDOM-SST-1G-44P-HL | 1GB        | Horizontal Right | -40°C ~+85°C    |

| DDOM-SST-1G-44P-H  | 1GB        | Horizontal Left  | -40°C ~+85°C    |

| DDOM-SST-1G-44P-V  | 1GB        | Vertical         | -40°C ~+85°C    |

| DDOM-SST-2G-44P-HL | 2GB        | Horizontal Right | -40°C ~+85°C    |

| DDOM-SST-2G-44P-H  | 2GB        | Horizontal Left  | -40°C ~+85°C    |

| DDOM-SST-2G-44P-V  | 2GB        | Vertical         | -40°C ~+85°C    |

## 2. Hardware Information

#### 2.1 Pin Assignment

| Pin # | Pin Name | Pin Type | Pin # | Pin Name | Pin Type       |

|-------|----------|----------|-------|----------|----------------|

| 1     | -RESET   | Ι        | 2     | GND      | Ground         |

| 3     | Data 7   | I/O      | 4     | Data 8   | I/O            |

| 5     | Data 6   | I/O      | 6     | Data 9   | I/O            |

| 7     | Data 5   | I/O      | 8     | Data 10  | I/O            |

| 9     | Data 4   | I/O      | 10    | Data 11  | I/O            |

| 11    | Data 3   | I/O      | 12    | Data 12  | I/O            |

| 13    | Data 2   | I/O      | 14    | Data 13  | I/O            |

| 15    | Data 1   | I/O      | 16    | Data 14  | I/O            |

| 17    | Data 0   | I/O      | 18    | Data 15  | I/O            |

| 19    | Ground   | Ground   | 20    | NC       | Not            |

| 17    | Oloulia  | Olouliu  |       |          | connect        |

| 21    | REQ      |          | 22    | GND      | Ground         |

| 23    | IOW      | Ι        | 24    | GND      | Ground         |

| 25    | IOR      | Ι        | 26    | GND      | Ground         |

| 27    | IORDY    | О        | 28    | GND      | Ground         |

| 29    | ACK      |          | 30    | GND      | Ground         |

| 31    | INTRQ    | О        | 32    | IOCS16   | 0              |

| 33    | SA1      | Ι        | 34    | CBLID    | I/O            |

| 35    | SA0      | Ι        | 36    | SA2      | Ι              |

| 37    | CS0      | Ι        | 38    | CSI      | Ι              |

| 39    | LED      | I/O      | 40    | GND      | Ground         |

| 41    | VCC      | Power    | 42    | VCC      | Power          |

| 43    | GND      | Ground   | 44    | NC       | Not<br>connect |

| Signal Name    | Dir. | Pin      | Description                                                                                                                                                                                                         |  |

|----------------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET          | Ι    | 1        | This pin Host Reset. Reset signal is from the host<br>and it is active low.                                                                                                                                         |  |

| Data<br>[15:0] | I/O  | 3-18     | These lines carry Data, Command and Status<br>information between the host and controller.D0 is<br>LSB and D15 is MSB.                                                                                              |  |

| IOW            | Ι    | 23       | The I/O Write Storable pulse is used to clock I/O<br>data on the Data bus into the controller registers.<br>The clocking will occur on the negative to the<br>positive edge of the signal (trailing edge).          |  |

| IOR            | Ι    | 25       | This is an I/O Read strobe generated by the host.<br>This signal gates I/O data into the bus from the<br>controller. The clocking will occur on the negative to<br>the positive edge of the signal (trailing edge). |  |

| IRQ            | 0    | 31       | This is an interrupt request from the controller to<br>host, asking for service. The output of this signal is<br>tri-state when the interrupt are disabled by the host.                                             |  |

| A[2:0]         | Ι    | 33,35,36 | A[2:0] are used to select the one of eight registers in the Task File.                                                                                                                                              |  |

| CSO,CS         | Ι    | 37,38    | -CSO is the chip select for the task file registers<br>while –CS1 is used to select the Alternate Status<br>Register and the Device Control Register.                                                               |  |

| IORDY          | 0    | 27       | This signal is negated to extend the host transfer<br>cycle of any host register access (Read or Write)<br>when the device is not ready to respond to a data<br>transfer request.                                   |  |

| IOCS16         | 0    | 32       | This open drain output signal is asserted low by the controller to indicate to the host the current cycle is a 16-bit (word) data transfer.                                                                         |  |

### 2.2 Signal Descriptions

| PDIAG | I/O | 34                             | This bi-directional open drain signal is asserted by<br>the slave after an Execute Diagnostic command to<br>indicate to the master it has passed its diagnostics.                          |

|-------|-----|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DASP  | I/O | 39                             | This open drain output is asserted low any time the<br>drive is active. In a Master/Slave configuration, this<br>signal is used the slave to inform the master which<br>has slave present. |

| GND   |     | 02,19,22,24,26,<br>28,30,40,43 | Ground                                                                                                                                                                                     |

| VCC   |     | 41,42                          | +5V or 3.3V Power                                                                                                                                                                          |

#### 2.3 System Power Consumption

| Dc Input Voltage (VCC) |                      | 3.3V / 5V ±5% |

|------------------------|----------------------|---------------|

| +5V Current            | Maximum active mode: | 150mA         |

# 3. Product Model and Physical Specification

#### 3.1 44 Pin Horizontal Right Side

#### 3.2 44 Pin Horizontal Left Side

## Warranty

This product is warranted to be in good working order for a period of one year (12 months) from the date of purchase. Should this product fail to be in good working order at any time during this period, we will, at our option, replace or repair it without additional charge except as set forth in the following terms. This warranty does not apply to products damaged by misuse, modifications, accident or disaster. Vendor assumes no liability for any damages, lost profits, lost savings or any other incidental or consequential damage resulting from the use, misuse of, originality to use this product. Vendor will not be liable for any claim made by any other related party. Return authorization must be obtained from the vendor before returned merchandise is accepted. Authorization can be obtained by calling or faxing the vendor and requesting a Return Merchandise Authorization (RMA) number. Returned goods should always be accompanied by a clear problem description. Should you have questions about warranty and RMA service, please contact us directly.

#### **ICOP** Technology Inc.

Address: No. 15 Wugong 5th Road, Xinzhuang Dist. New Taipei City, Taiwan (R.O.C.) 24890 TEL: +886-2-8990-1933 FAX: +886-2-8990-2045 Mail: info@icop.com.tw Website: http://www.icop.com.tw